设计人员所面临的挑战是,由于已经有了智能手机体验,用户期待这些产品能有同样高性能的触控用户界面。如果触控界面对输入响应延迟太长、无法对多次触摸做出一致的响应、或者被触控界面上的水干扰,无疑会让用户对设备的信任大打折扣。

为应对这一挑战,瑞萨电子推出了RL78/G23、RX140、RX130、RA2L1、RA2E1等多个入门级系列通用MCU,它们通过硬件实现了第二代瑞萨电容式触摸感应技术(简称CTSU2)。

CTSU2除了支持Button、Slider、Wheel等传统的触摸方式之外,还能够执行触控界面的接近式传感、快速并行扫描、自动扫描、多电极连接,从而实现触摸板、3D手势识别等高级应用。

下面简要介绍瑞萨电容式触摸感应技术CTSU2的自容式检测原理

自容式概述

图1-1所示为电极中产生的自电容。自电容式按键中连接到电容传感器的单个电极将测量电容量C。C的值是由电极及其周围导体形成的寄生电容Cp和由电极及手指形成的寄生电容Cf的复合值。电容的大小可以通过电容方程式计算 图片(参见Note部分)。由于周围的器件是静态的,因此Cp是常量,但Cf会随着手指的靠近而增加。通过设置Cf增加量的阈值,可以确定触摸按键是处于“打开”还是“关闭”状态。请注意,如果手指直接接触电极,则会导致电极短路,并且无法再测量电容。通常,电极和手指之间有几毫米厚的覆盖面板。

Note

C:电容,ε:相对介电常数,S:电极的正对面积,d:电极间距

图1-1 电极中产生的自电容示意图

CTSU2自容式检测原理

图2-1所示为自电容方式的CTSU2内部配置概览。CTSU2输出一个与所连接电极的电容量C成正比的数字计数值,并通过软件确定触摸按键是处于“打开”还是“关闭”状态。连接到CTSU2时,电极会充当由传感器驱动脉冲控制的开关电容,并从充放电电流来估测C的电容。CTSU2测量模块具有电流-频率转换功能,输入与充放电电流等效的电流,并输出与电流量成比例的频率。

图2-1 自电容CTSU2内部配置概览

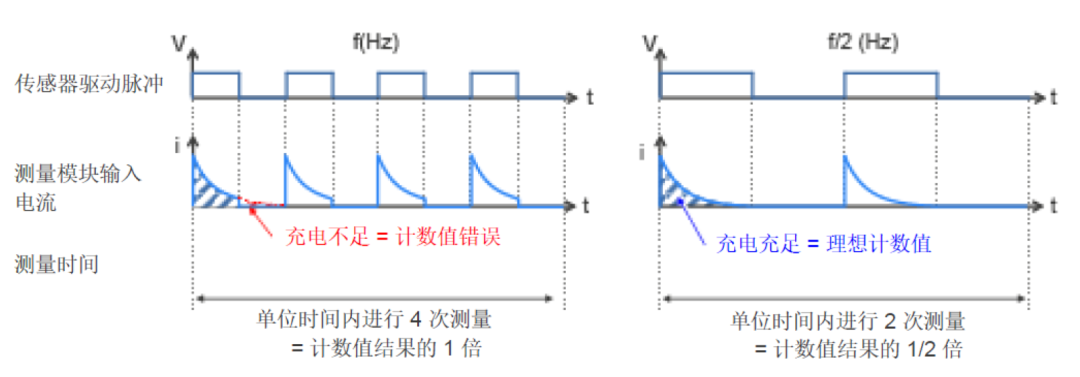

图2-2所示为CTSU2测量结果的示意图。当传感器驱动脉冲频率的一个周期比C充放电时间短且充放电不足时,则没有足够的电流流向C,因此计数值小于理想值。当寄生电容很大时,可以通过降低传感器驱动脉冲频率来进行测量。当传感器驱动脉冲频率降低时,CTSU2可测量的最大值为50pF。请注意,当传感器驱动脉冲频率降低时,电流-频率转换功能在单位时间内的测量次数也会减少,电极的灵敏度也可能会降低。可以通过调整CTSU2中的寄存器设定值来增加单位时间,但完成测量所需的时间也会增加。在设计电容式电极电路时,必须均衡考虑按键灵敏度、测量时间和抗噪性等条件。

图2-2 CTSU2测量结果示意图