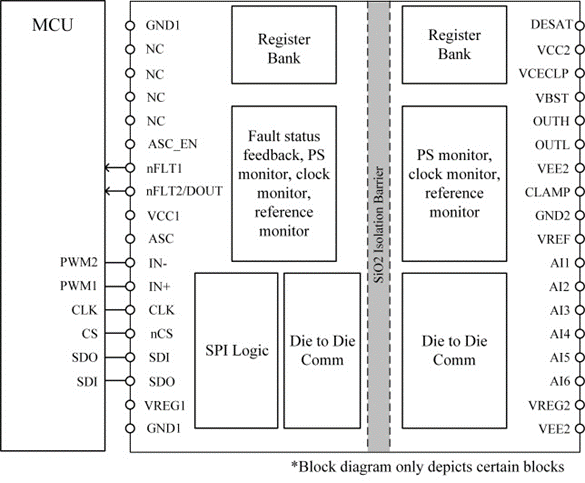

TI推出的功能安全栅极驱动UCC5870-Q1,旨在帮助客户实现电驱系统功能安全ASIL-D等级。其内部集成了丰富的保护以及诊断机制,对栅极驱动器本身以及开关管进行保护,可优化设计成本,简化设计复杂度。本文将对UCC5870-Q1内置的这部分诊断保护机制进行概述。

栅极驱动器保护

对UCC5870-Q1本身进行监控保护的机制主要是过温警示(TWN),热关断(TSD)以及丰富的内部自检(BIST)。

过热保护(TWN和TSD)是在IC上电后运行过程中持续监控的。分成原边和副边的TWN和TSD。其中,TWN是当die结温超过TWN_SET触发, 原副边可以分别使能。TWN可以设置是否在nFLT2 pin 脚报警, 相应状态寄存器置位,但IC不会有其他保护动作。

TSD是当die温度升到更高,超过TSD_SET时触发的。其中当原边TSD发生,IC会重新回到RESET状态,SPI无法通讯,输出被拉低。而副边TSD,类似地,输出会直接被拉低。但此时nFLT1如果没有被设置成屏蔽状态,则拉低,而且仍然可以通过SPI通讯,此时可能读取到相应的错误状态寄存器置位(由于TSD后副边电路被关断而导致原副边通讯中断,副边热关断的状态位可能没有被置位,此外,由于副边电路已经关断,可能会伴随时钟以及内部通讯故障状态位置位)。只有当IC冷却到阈值,如果是副边TSD,则还需要重新上下电VCC2,再重新完成上电初始化流程,IC才能重新输出。

UCC5870-Q1作为TI Functional Safety-Compliant的器件,集成了丰富的内部自检(BIST),它是一种对内部诊断保护机制本身作诊断的机制。可以分成电源轨保护机制自检(ABIST),以及各项保护的功能自检(Function BIST)。运行时,会内部模拟故障的产生,来诊断相应的保护是否按要求动作。

其中,ABIST会在IC上电时自动完成,期间会模拟VCC1, VCC2, VEE2以及内部电源轨的过欠压条件,此时在外部无法测试到电源电压的波动。如果内部比较器逻辑错误,没法准确检测到故障状态,则会有相应Analog BIST fault状态位置位,而且IC输出拉低。

功能自检是针对内部其他功能性的保护机制,比如DESAT, INP, STP, GM, SCP/OCP, PS_TSD, VCECLP等保护功能。这些自检需要手动写CONTROL*寄存器相应位来执行模拟故障的过程。可以在CONFIGURATION 2模式或者 ACTIVE模式执行相应的自检。

功率开关管保护

UCC5870-Q1 同时集成了丰富的安全机制,对功率开关管进行相关诊断和保护。包括过流/短路和过温类的保护(OCP, SCP, DESAT, 功率管热关断),关断类的保护(2LTOFF, STO, VCE CLAMP, internal and external MILLER CLAMP), 输入输出状态检测和保护(Gate monitor, STP),另外,还有TI 特有的开关管健康状态监控。

过流/短路保护

首先,过流和短路保护的关键,是在开关管短路耐受时间(SCWT)内,关断开关管,避免短路产生的热量把开关管损坏。同时兼顾防止误动作,功率耗散,高精度,低成本,设计简易等要点。

OCP和SCP是基于检测流过分流电阻器上的电流压降而判断的过流/短路保护机制。通过UCC5870-Q1集成的ADC通道(AI2, AI4, AI6)采样,可根据选用的功率开关管和分流电阻器的实际参数,设定不同的消隐时间,阈值电压。为了降低损耗和寄生参数的干扰,通常这种保护机制不直接检测著主功率电路的电流,而是检测集成了电流镜的功率开关(senseFET)管按比例缩小后的电流。而集成了senseFET的功率模组则可能提高了系统的成本。

另一类过流保护机制,是退饱和短路保护。它是利用IGBT 超过VCE 转折电压,从饱和区进入有源区后,VCE电压迅速增大而集电极电流不随之增长的特点,直接检测VCE的转折电压,来判断短路事件。其中,VCE转折电压和VGE电压有关, IGBT的正常工作VCE电压一般是1-3V,且转折电压较低,能通过简单的外围电路实现有效的过流保护。而相同规格的SiC Mosfet,由于其内部晶体(die)的面积更小,对关断时间的限制更苛刻,然而SiC Mosfet的转折电压通常却更高,同时,由于SiC Mosfet的高速开关特性,又需要较长的消隐时间来避免高噪声导致的误触发。因此,针对SiC Mosfet的退饱和过流保护的外围电路设计要求更苛刻。

关断类保护

短路保护时需要兼顾关断时高di/dt导致的过冲(overshoot)和关断损耗问题。为了实现可靠关断,UCC5870-Q1有多种关断方法。首先,短路保护和功率管热关断保护都可以灵活配置关断模式为软关断(STO)或者两级关断(2LTOFF)。其中,STO是将驱动的灌电流限制在设定的值,减缓关断斜率,从而减缓VCE 过冲。而如果STO无法满足限制过冲的目的,可考虑更激进的两级关断。它先按照设定灌电流值,把门级电压降至设定的平台电压,这个平台电压使开关管处于放大区,从而通过控制栅极电压控制住漏极电流。在平台区保持设定的时间,然后可选择通过软关断或者普通关断把平台电压放电至VEE。

有源钳位(VCECLP)则在正常运行过程中直接监控集电极电压,一旦VCE超过外围TVS管的雪崩击穿电压,且经过一定的消隐时间(由VCECLP pin脚外围的RC网络参数决定),则驱动能力由正常的灌电流降低至软关断电流值,并持续设定的时间,从而降低过冲电压。

而米勒钳位则是为了应对开关管正常关断时,由于高dv/dt耦合开关管寄生电容产生的米勒电流,流经驱动电阻导致IGBT VGE产生异常压降而重新误导通的问题。米勒钳位为米勒电流提供了低阻抗通路,使开关管即便在高速开关场景也能可靠关断。UCC5870-Q1提供的内部/外部米勒钳位配置选项,可灵活地针对不同的下拉能力需求,寄生参数以及layout设计来选择。

输入输出状态检测保护

为防止上下管直通而导致严重的烧毁,UCC5870-Q1集成STP来避免直通。PWM输入引脚分为IN+和IN-,且在同一组半桥驱动的配置中,上管驱动的IN+连接下管驱动IN-。当内部死区时间CFG1[TDEAD]设置成0,若IN+和IN-同时高电平,则报错,且按配置做相应保护动作。当内部死区时间CFG1[TDEAD]设置成大于0,则会在输出时自动插入相应的死区时间,避免直通。

为保证输入输出电平的一致性,UCC5870-Q1内部集成了2种PWM通道信号完整性检测机制。其中,GM_Fault机制是直接检测输出实际电压并转换成逻辑电平,与输入IN+逻辑电平比较。为了防止电平转换阶段误报,可灵活配置消隐时间。

开关管健康状态检测

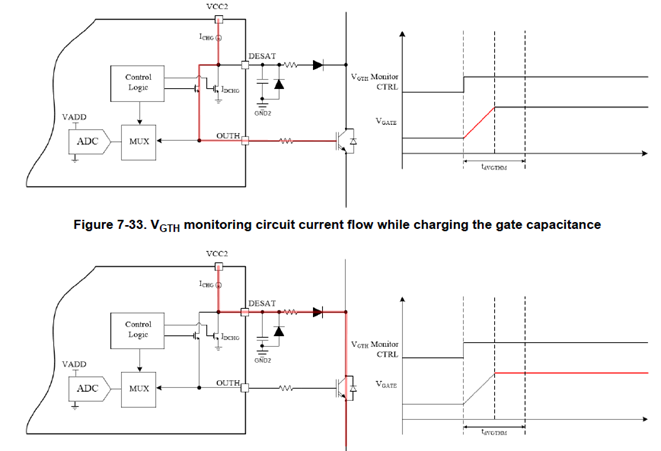

最后,介绍一下UCC5870-Q1特有的开关管健康状态检测。根据权威论文的实测数据[4],由于开关管导通阈值VGTH在考虑不同因数影响下,相对于开关次数展现出更清晰稳定的单调性趋势, VGTH是监控开关管健康状态的理想参数。而UCC5870-Q1集成的检测VGTH方法如下。当通过CONTROL2[VGTH_MEAS]位使能VGTH? 监控,则DESAT和OUTH间的开关管导通,给外部功率开关管门级恒流充电。当门级电压达到导通阈值VGTH ,主功率开关管开始导通,内部恒流源电流换流,全部流经DESAT pin脚外部二极管和功率开关管,即门级电压被自动钳位在VGTH 。内部ADC从使能命令开始经过固定的消隐时间tdVGTHM后即可采到实时的开关管VGTH。MCU根据采回的实时VGTH即可判断实时开关管的健康状态。

总结

UCC5870-Q1集成了丰富强大的保护功能,可靠保护开关管以及驱动芯片在复杂而恶劣的电驱环境中运行。本文对这些保护功能的设计目的,触发条件,保护逻辑以及相关配置进行了说明,有助于工程师全面了解UCC5870-Q1的特点。