TAS2505-Q1 是一款支持数字和模拟输入的车规级D类功率放大器,其输出功率可达2.6W。内部集成了LDO,能够单电源供电,简化了供电电路的设计。除此之外,TAS2505-Q1内部还集成了DSP功能,使得此芯片对音频有一定的处理能力,更进一步地简化了电路设计。此芯片还提供I2C&SPI数字通信接口,价格便宜,满足低成本的设计要求。在过去的10多年内得到了市场的广泛认可,有良好的口碑,是汽车仪表盘、紧急呼叫(eCall)和远程通信应用的理想选择。

本文分析了TAS2505-Q1连接扬声器偶发没有声音情况,总结了常见的可能原因,并提供具体的排查方向和解决措施。

故障描述

在TAS2505-Q1的应用案例中,出现问题的状况主要表现为上电后偶发扬声器没有声音,其对应的TAS2505-Q1的 输出端SPKP & SPKM没有输出。出现这个问题的情况应当从硬件方向和软件方向考虑。

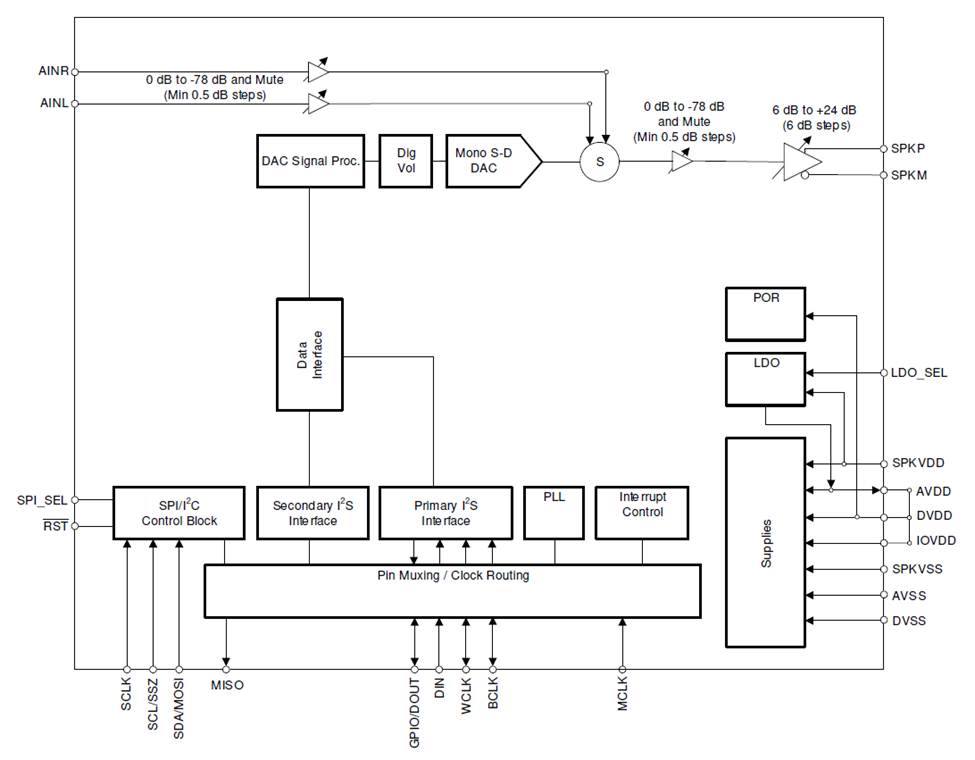

图1. TAS2505-Q1框图

硬件方向

上电时序以及电源稳定性,时钟状态,输出端是否过流

1. 上电时序以及电源稳定性

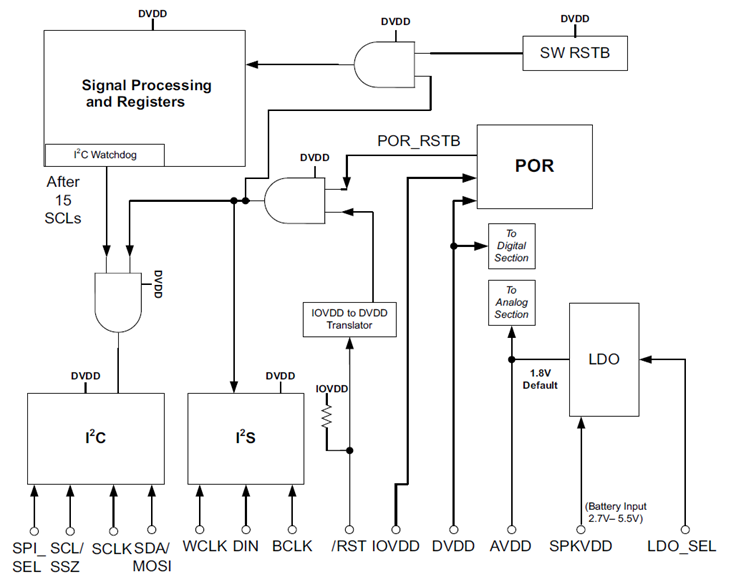

图2. TAS2505-Q1内部框图

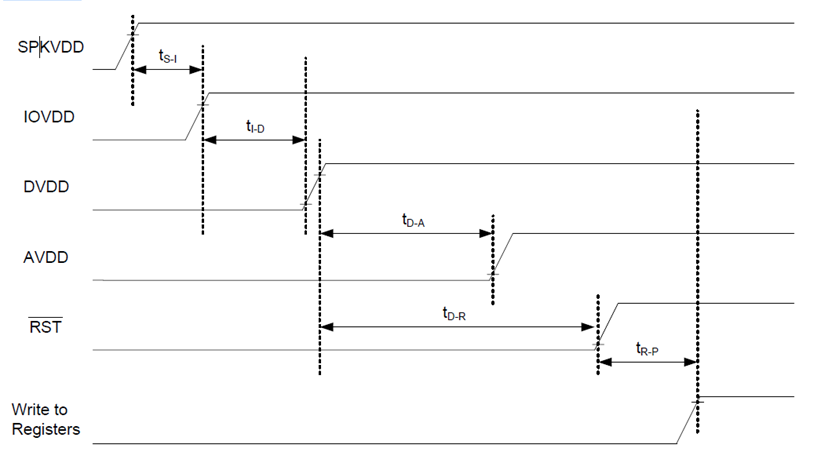

A: AVDD和IOVDD的是否是同一个电源,其时序如下图,SPKVDD>IOVDD>AVDD/DVDD>RST>IIC指令。且需要满足如图,的时间间隔要求。

图3 AVDD和IOVDD同电源上电时序要求

表1 AVDD和IOVDD同电源上电时序间隔时间

B: AVDD和IOVDD不是同一个电源,其时序如下图,SPKVDD>IOVDD>AVDD>DVDD>RST>IIC指令。

表2 AVDD和IOVDD不同电源上电时序间隔时间

排查时需要注意除了对应的时序,还需要检查各个电源轨是否电压工作正常,如AVDD/DVDD是否在上电时达到了1.8V。AVDD及DVDD分别是对内部的模拟器件和数字电路供电,支持1.8V供电,如果此电源供电不稳定,那么芯片内部的寄存器和DAC等工作状态就不可控,也会出现TAS2505-Q1没有输出的情况。在实际应用中,简化电路可将AVDD和DVDD采用一个1.8V电源共同提供(建议使用外部LDO 而不是 TAS2505-Q1 的内部 LDO)。对应电源电压如表3。

表3. TAS2505-Q1电源要求

如果在上电过程中不满足时序和电平要求会导致TAS2505-Q1初始化失败,偶发出现TAS2505-Q1的输出端为低电平,从而导致扬声器无声故障。

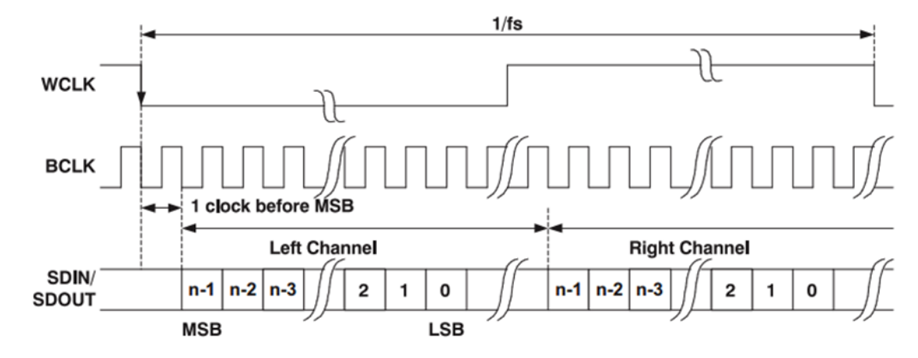

2. 时钟状态

TAS2505-Q1的内部时钟和I2S时钟,DAC参考内部时钟,其中内部时钟有两种来源——BCLK (Audio serial bit clock) 和MCLK (External master clock),内部选择其中一个即可。BCLK是模块内的同步信号,TAS2505-Q1的BCLK即可以由外部提供,也可以由芯片提供(此时就需要使用MCLK)。内部PLL的输入由BCLK/MCLK分频得出,如果BCLK/MCLK工作不稳定,内部PLL也会不稳定,尤其在使用IIC/SPI对芯片寄存器进行操作时,就可能导致芯片访问异常,从而发生TAS2505-Q1工作不正常的情况,其外部表现为偶发没有声音输出。所以在访问芯片过程中需要保证IIC/SPI信号接收/发送时BCLK/MCLK稳定。

3. 输出端是否过流

通常 Class D 功放芯片都会设计有过流保护功能,在输出电流超过限流阀值后芯片自动关闭驱动信号停止输出。一般的过流保护是由于输出功率超过额定或者输出短路而引起。还有一种特殊的过流保护现象是由于高次谐波能量过大引起。高次谐波过流保护是一种特殊的过功率现象。通常用户的电路设计完全正确,常规功率测试未超过额定功率。这种保护具有以下几个特征:

● 问题机器在1KHz 标准音频信号测试时输出功率并未超过最大输出功率。

● 播放高频成分较多的歌曲较容易出现保护。

● 使用水泥电阻代替喇叭作为负载,保护现象消失。

● 减小,或者去掉输出LC 滤波器的电容,保护现象消失。

解决方法:

减小 LC 滤波器网络的电容C 的值可以增大LC 滤波器的截止频率。使得截止频率远大于高次谐波可能达到的频率。通常将电容值减小5 倍以上即可有效抑制高次谐波过流保护的问题。

优点:无需修改电路,只需要修改参数值。

缺点:LC 网络滤波效果变差,开关纹波增加,EMI 有可能恶化。

软件方向

1. 检查正常状态和异常状态寄存器的配置

找到其差异点,并针对差异点查阅规格书或应用指南,发现问题。

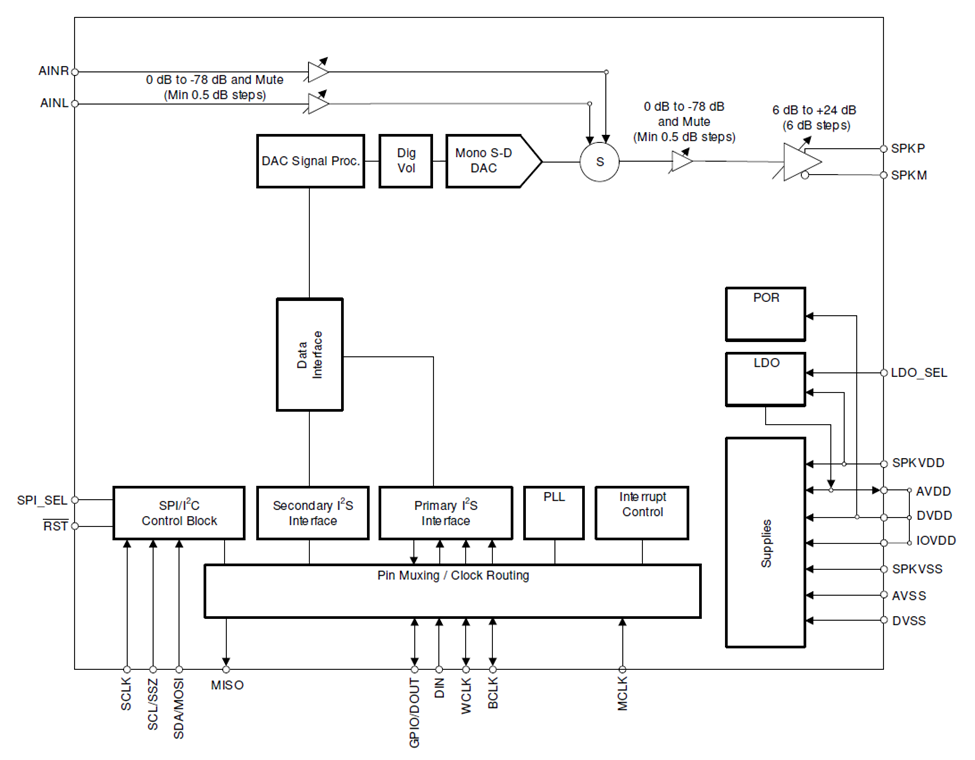

2. 软件初始化的寄存器配置

检查初始化软件配置,需要保证DAC(P0, R63, D7 = 1, D5-D4 = 01, D3-D2 =00, D1-D0=00)开启后, 再开启CLASS-D(P1, R45, D1=1) , 如图6。如果顺序错误会导致初始化的时候失败, 芯片内部工作不正常, 偶发TAS2505-Q1无输出, 扬声器没有声音。

调查举例

案例的故障描述如下:

WHAT: 车辆启动后不出声音, TAS2505-Q1设计在仪表盘板卡中,车辆启动后应当有对应的提示音。

WHO: 车厂测试工程师

WHEN: 车辆0km测试过程中

WHERE: 车厂 + 汽车仪表供应商

HOW: 车辆冷启动的时候,本来仪表会通过 TAS2505-Q1发出开机提示音。但是没有发生声音。后测量其TAS2505-Q1的SPKP&SPKM,发现在出问题时没有输出,正常情况下有稳定的方波输出,车厂进行ABA后故障跟随芯片。

HOW MUCH:出现此情况的芯片复现的概率为30%。

故障分析

1.主控平台在异常状态和正常状态均有正常的I2S输出,且芯片和SPKP&SPKM没有输出,故排除异常状态由主控平台未给出音频导致,推断为芯片工作状态不正常。

2. 芯片进入过压过流过温等保护状态,芯片异常状态下,环境温度30℃,板卡工作温度50℃,且芯片的供电:SPKVDD = 5V; IOVDD = 3.3V; AVDD = DVOO = 1.8V; 电压工作正常。

排查如下:

硬件方向:

● 确认是否出现输出过流保护,检查输出外部电感和电容。

结果:去除输出LC滤波电路,此现象仍然出现。

● 检查上电时序,测试结果符合上电时序要求,SPKVDD>IOVDD>AVDD/DVDD>RST>IIC指令。

软件方向:

查验寄存器配置 ,发现其故障原因是芯片在初始化过程中先打开了CLASS-D, 后打开DAC。正确顺序应该是先打开DAC再打开CLASS-D,修改为正确寄存器顺序后,高低温压测1000次,故障未在出现。

故此次故障的原因为 :芯片初始化过程中颠倒了 CLASS-D和 DAC开启顺序,从而导致芯片偶发初始化失败。

总结

本文分析了TAS2505-Q1在应用过程中出现问题的原因,并且从硬件和软件方向提出了故障排查指南,并给出相应的优化措施,有助于工程师在设计出鲁棒性更强的音频系统。同时,有助于工程师在遇见相似问题时能够更高效地排查故障 。另外,给出一个实际用例,供大家参考。

参考文献

TAS2505-Q1 2.6-W Digital/Analog Input Automotive Class-D Speaker Amplifier With Audio Processing datasheet (Rev. C)

TAS2505 Application Reference Guide

TAS25xx Codec Control EVM (Rev. A)

Automotive Diagnostics Using TAS2505-Q1 (Rev. C)

来源:TI