本文解释三种主要类型的多谐振荡器电路以及如何构建每种电路。多谐振荡器电路一般由两个反相放大级组成。两个放大器串联或级联,反馈路径从第二放大器的输出接回到第一放大器的输入。由于每一级都将信号反相,因此环路整体的反馈是正的。

多谐振荡器主要分为三种类型:非稳态、单稳态和双稳态。非稳态多谐振荡器使用电容耦合两个放大器级并提供反馈路径。电容会阻隔任何从一级传送到下一级的直流信号,因此非稳态多谐振荡器没有稳定的直流工作点,是一个自由运行的振荡器。在单稳态多谐振荡器中,从一级到另一级的耦合使用一个电容,而第二个连接是通过直流路径。因此,单稳态多谐振荡器有一个稳定的直流级。除了施加触发脉冲时之外,电路均保持这种单一的稳定状态。然后,状态改变,持续时间为信号路径的交流耦合部分的RC时间常数所设置的预定时长。在双稳态多谐振荡器中,两条耦合路径都是直流耦合,因此电路具有两种不同的稳定状态,并且不使用电容。双稳态多谐振荡器也被称为触发器,在任一时间处于两种直流稳定状态中的一种状态。

非稳态多谐振荡器

目标

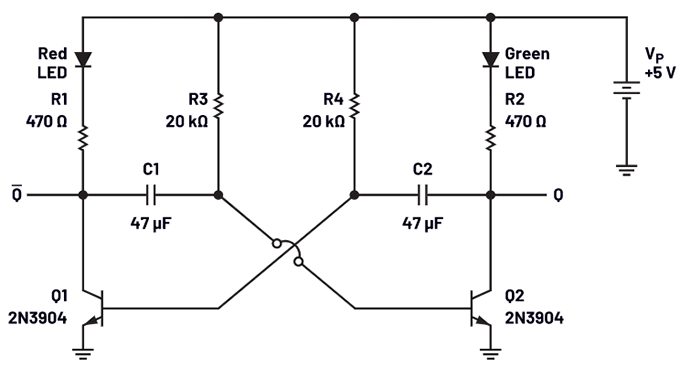

第一个实验的目的是构建一个非稳态多谐振荡器。两个相同的电阻电容网络决定振荡发生的频率。放大器件(晶体管)以共发射极配置连接,如图1所示。

图1. 非稳态多谐振荡器

材料

● ADALM2000 主动学习模块

● 无焊试验板

● 跳线

● 两个470 Ω电阻

● 两个20 kΩ电阻

● 两个小信号NPN晶体管(2N3904)

● 一个红光LED

● 一个绿光LED

● 两个47μF电容

说明

在无焊试验板上构建图1所示电路。请注意,ADALM2000板没有输入,只有电源。第一个反相放大器级由Q1、R1和用作输出负载的红光LED组成。第二个反相放大器级由Q2、R2和用作负载的绿光LED组成。C1将位于Q1集电极的第一级输出耦合到位于Q2基极的第二级输入。类似地,C2将位于Q2集电极的第二级输出耦合回位于Q1基极的第一级输入。

硬件设置

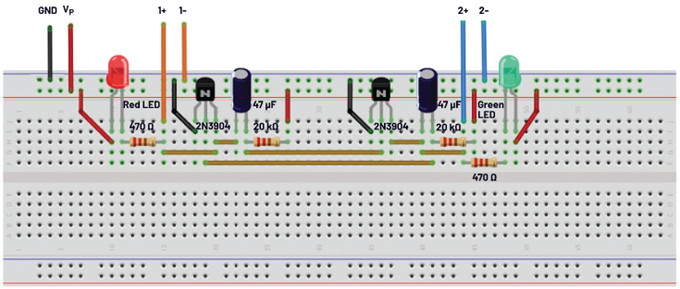

试验板连接如图2所示。

图2. 非稳态多谐振荡器试验板电路

程序步骤

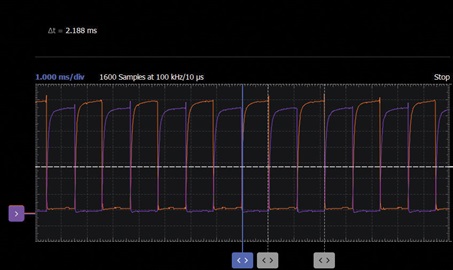

只有在电路构建完毕并检查之后,才能开启VP电源。红光和绿光LED应以大约1秒的间隔交替闪烁。您还可以使用示波器通道监视输出波形(Q和Q-bar)。

由于电容C1和C2的值较大,因此振荡频率非常慢。将C1和C2替换为0.1 μF电容。电路现在应该以快得多的速度振荡,两个LED同时亮起。现在使用示波器通道测量输出波形的频率和周期。

图3. 使用47 μF电容时的非稳态多谐振荡器间隔

图4. 使用0.1 μF电容时的非稳态多谐振荡器间隔

单稳态多谐振荡器

目标

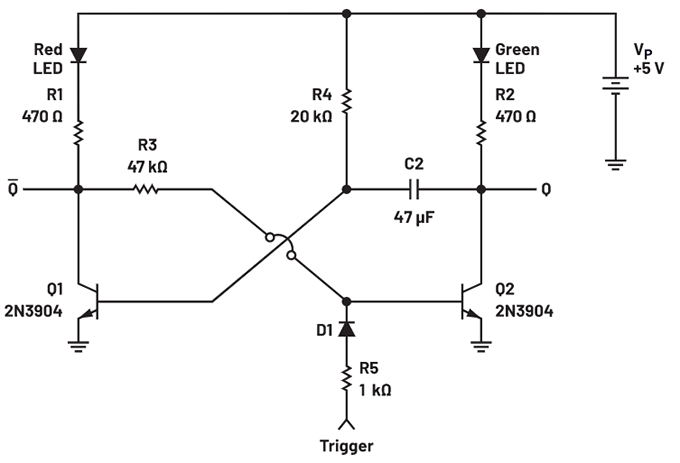

第二个实验的目的是构建一个单稳态多谐振荡器。一个电阻电容网络决定单稳态多谐振荡器输出的持续时间。放大器件(晶体管)以共发射极配置连接,如图2所示。

材料

● ADALM2000主动学习模块

● 无焊试验板

● 跳线

● 两个470 Ω电阻

● 一个1 kΩ电阻

● 一个20 kΩ电阻

● 一个47 kΩ电阻

● 一个小信号二极管(1N914)

● 两个小信号NPN晶体管(2N3904)

● 一个红光LED

● 一个绿光LED

● 一个47 μF电容

说明

在无焊试验板上构建图5所示电路。从实验1中的电路出发,移除一个20 kΩ电阻(旧R3),将电容C1替换为47 kΩ电阻(新R3)。在Q2的基极上添加二极管D1和电阻R5,如图所示。务必将C2替换为原来的47 μF电容。

图5. 单稳态多谐振荡器

硬件设置

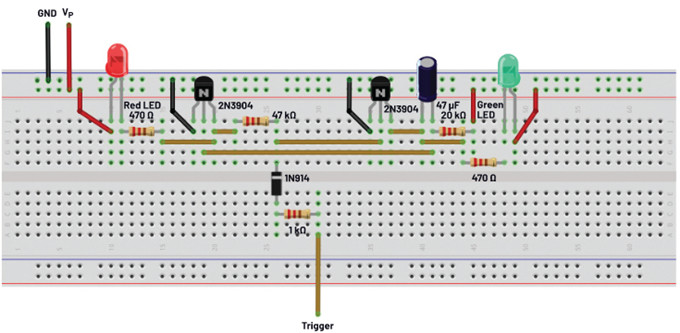

试验板连接如图6所示。

图6. 单稳态多谐振荡器试验板电路

程序步骤

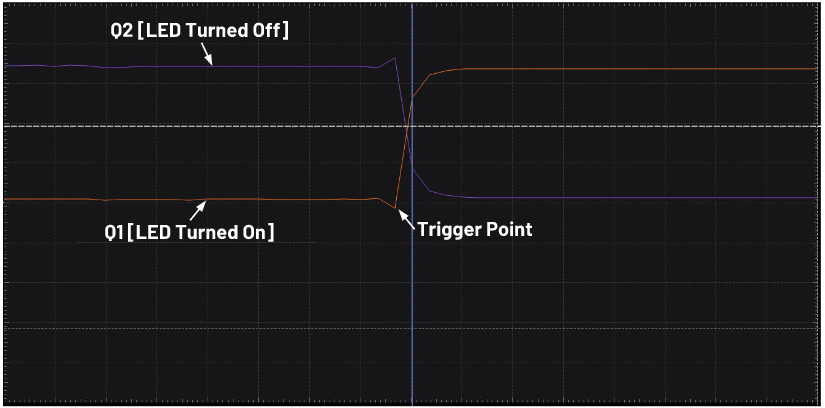

只有在电路构建完毕并检查之后,才能开启VP电源。红光LED应亮起,绿光LED应熄灭。用一段电线将触发器输入(R5端)短暂触碰VP,然后立即松开。红光LED应熄灭,绿光LED点亮约一秒钟,然后返回稳定状态,红光LED亮起,绿光LED熄灭。多试几次。

图7. 触发时的单稳态多谐振荡器行为

双稳态多谐振荡器(或触发器)

目标

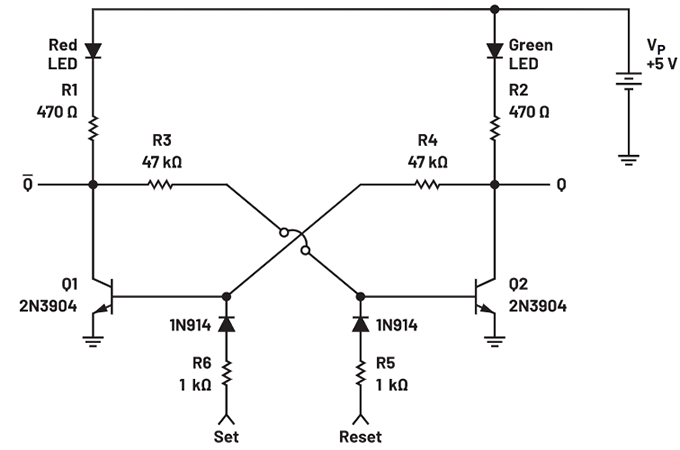

第三个实验的目的是构建一个双稳态多谐振荡器。放大器件(晶体管)以共发射极配置连接,如图8所示。

材料

● ADALM2000主动学习模块

● 无焊试验板

● 跳线

● 两个470 Ω电阻

● 两个1 kΩ电阻

● 两个47 kΩ电阻

● 两个小信号NPN晶体管(2N3904)

● 两个小信号二极管(1N914)

● 一个红光LED

● 一个绿光LED

说明

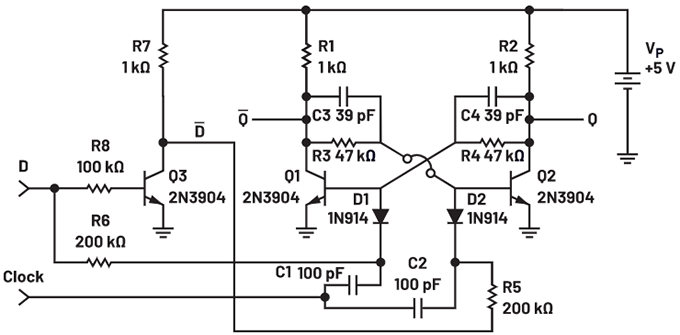

在无焊试验板上构建图8所示电路。

图8. 双稳态多谐振荡器

硬件设置

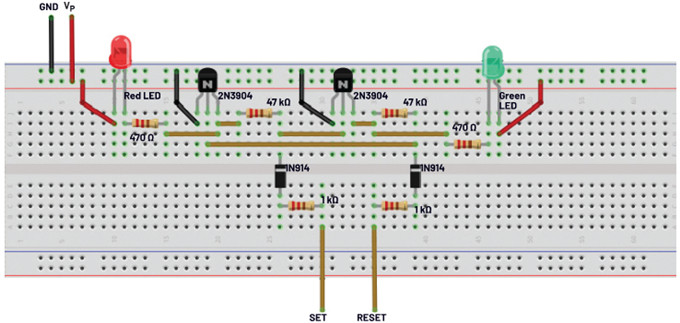

试验板连接如图9所示。

图9. 双稳态多谐振荡器试验板电路

程序步骤

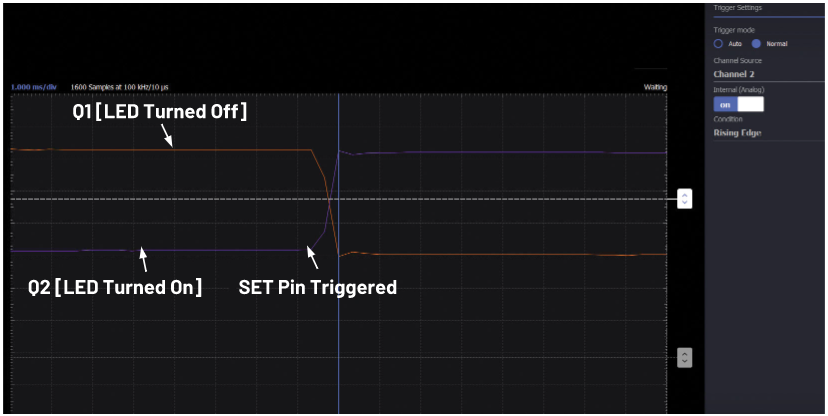

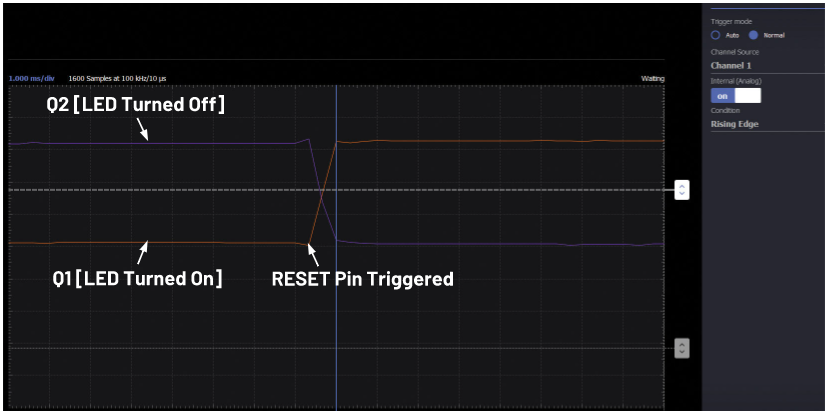

只有在电路构建完毕并检查之后,才能开启VP电源。红光LED应点亮而绿光LED熄灭,或者绿光LED应点亮而红光LED熄灭。用一段电线将SET或RESET输入(R5端或R6端)短暂触碰VP,然后立即松开。LED应改变状态或来回切换,具体取决于哪个输入触碰到VP。多试几次。

图10. 触发SET引脚的双稳态多谐振荡器行为

图11. 触发RESET引脚的双稳态多谐振荡器行为

D型触发器

目标

第四个实验的目的是使用实验3中的双稳态或SET-RESET触发器来构建所谓的D型触发器。

材料

● ADALM2000主动学习模块

● 无焊试验板

● 跳线

● 三个1 kΩ电阻

● 一个100 kΩ电阻

● 两个200 kΩ电阻

● 两个47 kΩ电阻

● 三个小信号NPN晶体管(2N3904)

● 两个小信号二极管(1N914)

● 两个39 pF电容

● 两个100 pF电容

说明

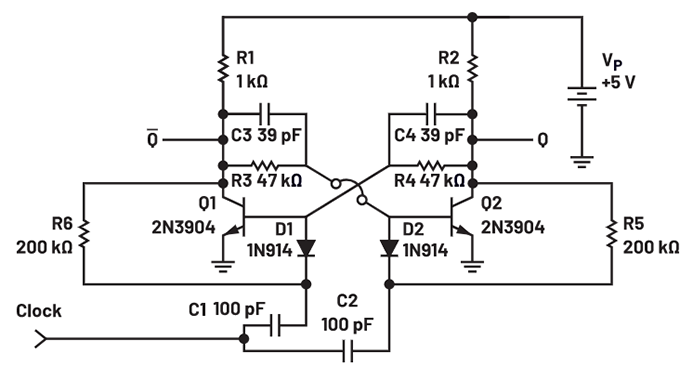

在无焊试验板上构建图12所示的D型触发器电路。请注意,与图8相比,两个二极管的极性相反。此实验将在高得多的频率下进行,因此LED已被移除,改用简单的1 kΩ负载电阻。

图12. D型触发器

触发器两种状态之间的切换是通过施加D(数据)信号和单个时钟脉冲来实现的:根据D输入相对于当前状态的状态,在时钟脉冲的负沿或下降沿,ON晶体管将断开,OFF晶体管将导通。真D信号和互补DB信号(Q3、R7反相级的输出)用于偏置二极管D1和D2,以将时钟脉冲引导至正确的基极,这相当于图8中的SET和RESET输入。

为了说明电路如何工作,我们假设电路处于两个稳定状态之一,QB输出低电平(Q1的集电极电压为0 V),Q输出高电平(Q2的集电极电压为5 V高电平)。当D输入为低电平(DB为高电平)时,D1的阴极(通过R6)具有低电压,其阳极(通过R4)具有高电压(导通晶体管Q1的VBE),使其正向偏置。D2的阴极(通过R5)具有高电压(来自DB),其阳极(通过R3)具有低电压(关断晶体管Q2的VBE),使其反向偏置。

由于D1正向偏置,所以时钟输入上的负向脉冲(通过C1和C2耦合)被引导至Q1的基极,但由于D2反向偏置,所以负向脉冲被Q2的基极阻隔。通过C3和R3并联组合的交叉耦合连接使Q1关断,并使Q2导通。由于我们之前在简单双稳态多谐振荡器中看到的正反馈效应,这种情况发生得非常快速。电路现在处于另一种稳定状态,Q输出高电平,QB输出低电平。电路将保持在该状态,直到D输入变为高电平并且另一个负向时钟脉冲到达之后。

硬件设置

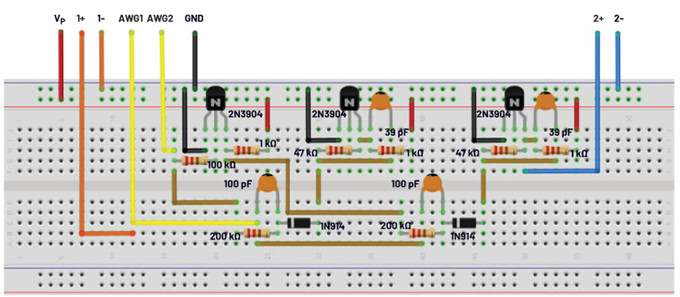

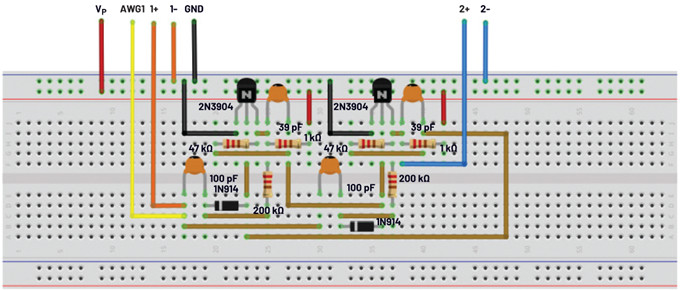

试验板连接如图13所示。

图13. D型触发器试验板电路

程序步骤

AWG1输出应连接到图12中标记的时钟输入。AWG2输出应连接到D输入。示波器通道1输入应连接到时钟输入。示波器通道2应连接到图12中触发器的Q输出。AWG1和AWG2均应配置为具有5 V幅度峰峰值和2.5 V偏移(0 V至5 V摆幅)的方波。将AWG1的频率设置为10 kHz,将AWG2的频率设置为5 kHz。将AWG2的相位设置为45度。务必将两个AWG输出配置为同步运行。

只有在电路构建完毕并检查之后,才能开启VP电源并使能AWG输出。应能在Q输出上观察到一个方波,其与时钟输入信号的下降沿对齐。更改AWG2(D输入信号)的相位,同时观察此对齐。这会随着D输入的相位变化而变化吗?将通道1示波器输入移至D输入。应能看到一个类似的方波信号,但它相对于Q输出超前。换言之,Q输出延迟到时钟信号的下降沿为止。

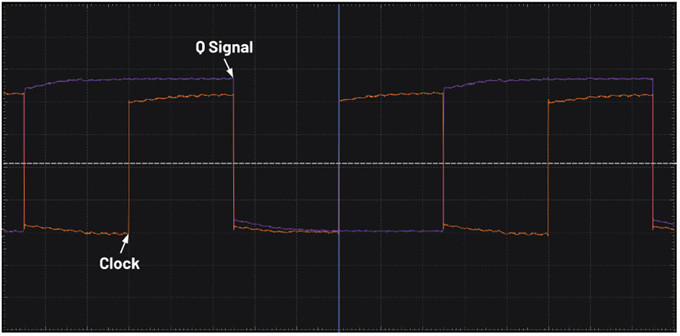

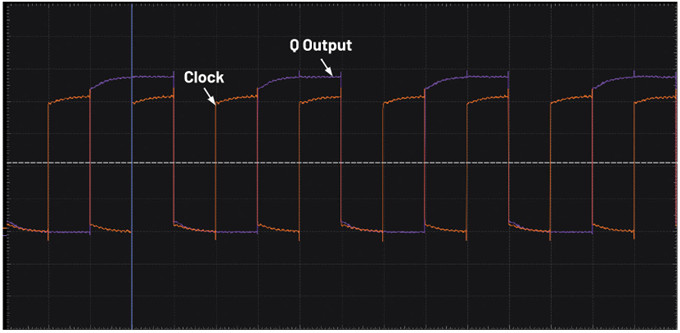

图14. Q和时钟信号图

图15. Q和D信号图

2分频触发器

目标

第五个实验的目的是修改实验4中的D型触发器,以构建一个将输入信号的频率除以2的电路。

材料

● ADALM2000主动学习模块

● 无焊试验板

● 跳线

● 两个1 kΩ电阻

● 两个200 kΩ电阻

● 两个47 kΩ电阻

● 两个小信号NPN晶体管(2N3904)

● 两个小信号二极管(1N914)

● 两个39 pF电容

● 两个100 pF电容

说明

修改实验4中的D型触发器,在无焊试验板上构建图16所示的2分频电路。

图16. 2分频电路

两种状态之间的切换是通过施加单个时钟脉冲来实现的;在该时钟脉冲的负沿或下降沿,这会导致ON晶体管断开,OFF晶体管导通。依次向每个基极施加脉冲,该电路将顺序切换,这是通过单个输入时钟脉冲来实现的——该时钟脉冲用于偏置两个二极管,根据触发器的当前状态将脉冲引导至正确的基极。

为了说明电路如何工作,我们假设电路处于两个稳定状态之一,Q1的集电极电压为低电平(0 V),Q2的集电极电压为高电平(5 V)。D1的阴极(通过R6)具有低电压,其阳极(通过R4)具有高电压(导通晶体管Q1的VBE),使其正向偏置。D2的阴极(通过R5)具有高电压,其阳极(通过R3)具有低电压(关断晶体管Q2的VBE),使其反向偏置。

由于D1正向偏置,所以外部负向脉冲(通过C1和C2耦合)被引导至Q1的基极,但由于D2反向偏置,所以负向脉冲被Q2的基极阻隔。通过C3和R3并联组合的交叉耦合连接使Q1关断,并使Q2导通。由于我们之前在简单双稳态多谐振荡器中看到的正反馈效应,这种情况发生得非常快速。

电路现在处于第二稳定状态,等待另一个负向时钟脉冲。

由于Q2的集电极电压(Q输出节点)会随着每个时钟脉冲改变状态,因此每出现两个时钟输入脉冲,输出端就会出现一个脉冲。因此,它可以用作二分频电路。

硬件设置

试验板连接如图17所示。

图17. 2分频触发器试验板电路

程序步骤

AWG1输出和示波器通道1输入均应连接到图16中标记的时钟输入。示波器通道2应连接到图16中触发器的Q输出。AWG1应配置为具有5 V幅度峰峰值和2.5 V偏移(0 V至5 V摆幅)的方波。将频率设置为10 kHz。

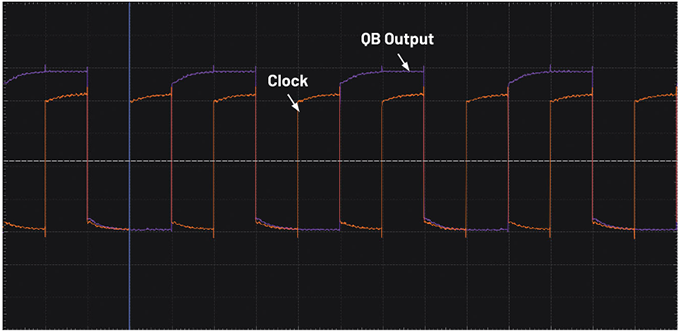

只有在电路构建完毕并检查之后,才能开启VP电源并使能AWG1输出。应能在Q输出上观察到一个方波,其频率是AWG1信号频率的一半。将通道2示波器输入移至QB输出。应能看到一个类似的方波信号,但它相对于Q输出反相。

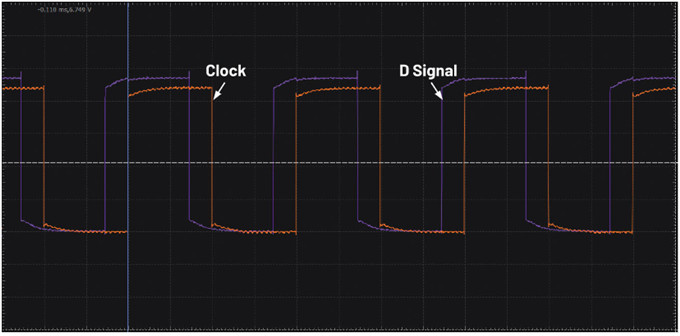

图18. 时钟和Q输出图

图19. 时钟和QB输出图

问题

对于图1所示电路,增加或减少两个电容的值会产生什么影响?

您可以在 学子专区 论坛上找到答案。

来源:ADI